#### **KR ERL**<sub>min</sub> Proposal

Richard Mellitz, Samtec

November 2019 IEEE 802.3 100 Gb/s, 200 Gb/s, and 400 Gb/s Electrical Interfaces Task Force Plenary Meeting Waikoloa, HI, USA

## ToC

- ☐ Device Test fixture

- ☐ ERL for device Clause 163.9

- ☐ ERL for channels Clause 163.10

- □ Recommendation

## Recommendation: Device test fixture TBD

- ☐ There is no published data to show the feasibility of reasonable 100G device test fixtures at TP0a or TP5a.

- □ Recommend ERL, modal return loess, and parameters using a pulse fit to be specific at TPO and TP5 as normative for draft 1.0

- If a test fixture is specified the data at tp0 and tp5 may be backed out to TP0a and TP5a at a later time.

- ☐ This implies de-embedding

- In most cases device vendors will own the test fixture which is different from the CR situation

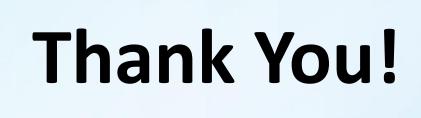

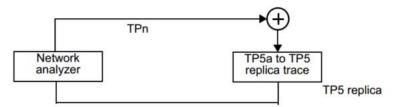

- The replace trace has little impact on Receive interference tolerance testing.

Figure 93C-5—Interference tolerance channel noise path test setup

Figure 93C-4—Interference tolerance channel s-parameter test setup

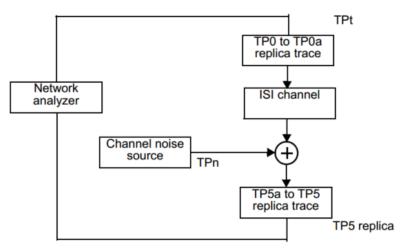

## Recall ERL pass/fail from mellitz\_3ck\_03a\_0919

# ERL<sub>min</sub> for channels (163.10.2)

| parameter                                                                       | Reference       | Value | Units |

|---------------------------------------------------------------------------------|-----------------|-------|-------|

| Transition time associated with a pulse                                         | T <sub>r</sub>  | 0.01  | Ns    |

| Incremental available signal loss factor                                        | $\beta_{x}$     | 2.4   | Ghz   |

| Permitted reflection from a transmission line external to the device under test | $\rho_{x}$      | 0.19  |       |

| Length of the reflection signal                                                 | N               | 3000  | UI    |

| Equalizer length associated with reflection signal                              | N <sub>bx</sub> | 12    | UI    |

ERL of the channel at TPO and at TP5 are computed using the procedure in 93A.5 with the values in the table above

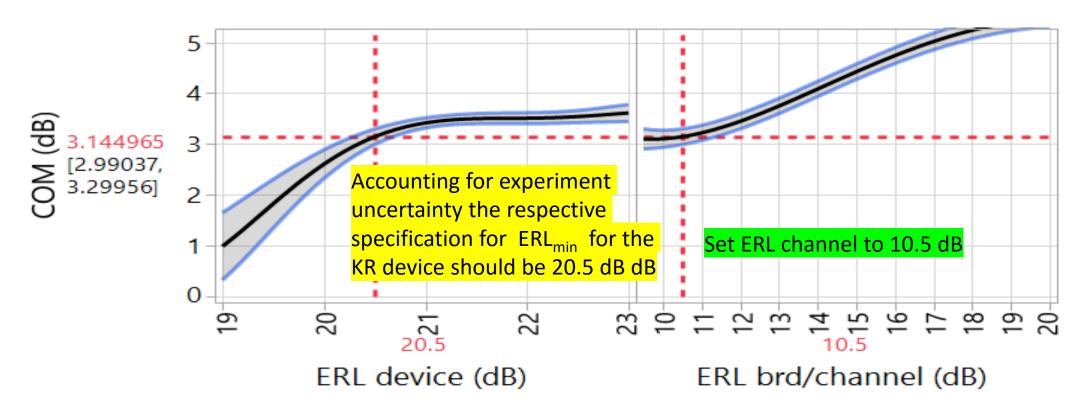

Channel ERL at TPO and at TP5 shall be greater than or equal to 10.5 dB.

# Setting ERL for the channel help suggest ERL for the device as shown in mellitz\_3ck\_adhoc\_02\_100219

Data from 2596 channel/package length cases

N<sub>bx</sub> chosen to be 24 in also suggested in mellitz\_3ck\_adhoc\_02\_100219

## ERL for devices (163.9.3.1 and 169.9.4.1)

| parameter                                                                       | Refere<br>nce   | Value | Units |

|---------------------------------------------------------------------------------|-----------------|-------|-------|

| Transition time associated with a pulse                                         | T <sub>r</sub>  | 0.01  | Ns    |

| Incremental available signal loss factor                                        | $\beta_{x}$     | 2.4   | Ghz   |

| Permitted reflection from a transmission line external to the device under test | $\rho_{x}$      | 0.3   |       |

| Length of the reflection signal                                                 | N               | 3000  | UI    |

| Equalizer length associated with reflection signal                              | N <sub>bx</sub> | 24    | UI    |

ERL of the channel into a device at TPO and at TP5 are computed using the procedure in 93A.5 with the values in the table above

Channel ERL at TPO and at TP5 shall be greater than or equal to 20.5 dB.

## Recommendation

Until better data for actual products is available

☐ Use slide 5 and 7 for the KR ERL baseline